# PULSE

# Dangerous assumptions in modern Product Security

Cristofaro Mune (c.mune@pulse-sec.com**)** @pulsoid

- Cristofaro Mune (@pulsoid)

- Product Security Consultant/Researcher

- Keywords: TEE, IoT, Devices, HW, Fault Injection, Exploitation,...

- *(Public)* Research:

- [2009] "Hijacking Mobile Data connections"

- [2010] AP Exploitation

- [2015] Breaking WB cryptography

- [2017]:

- TEEs secure initialization

- IoT exploitation

- Linux Privilege Escalation with Fault Injection

### **Devices and markets**

I Contraction

Physical Security

Networking

Mobile devices

#### Smart homes

Mobile Payments

Automotive

#### Replying to @joshikml Its my wallet. I am CEO of BitFi 2:15 PM - 20 Jul 2018

# iPhone X components and suppliers (some)

#### Accelerometer

# Bosch & Ivensense Baseband Processor

#### Qualcomm Batteries

Samsung & Shenzhen Desay Battery Technology

#### Chips

Cirus Logic, Samsung, TSMC, MicroSemi, Broadcom & NXP

#### DRAM

TSMC & SK Hynics

#### eCompass

Alps Electric

# **Example: Apple suppliers 2018**

#### Where Apple suppliers are headquartered (number of companies) Saudi Arabia 1 Singapore 5 Hong Kong South Korea Taiwan EU, Switzerland, 51 15 UK Total 27 China-200 43 39 Japan U.S.

Source: Apple's list of suppliers for 2018

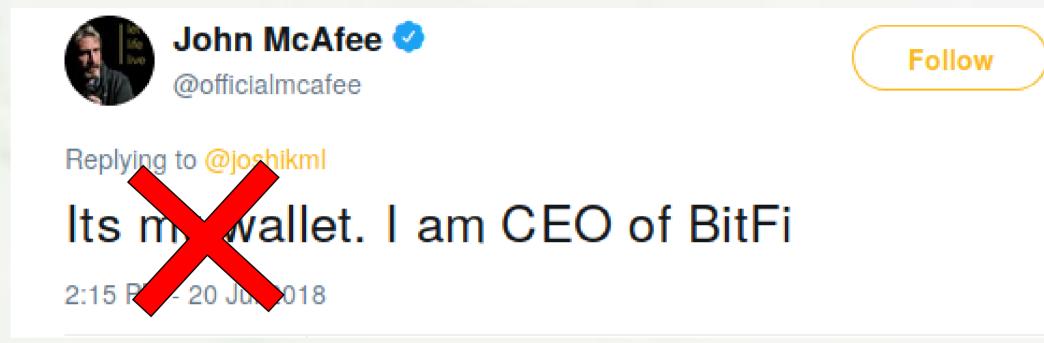

Who owns a device?

### "Nobody.

Really, nobody FULLY owns a device."

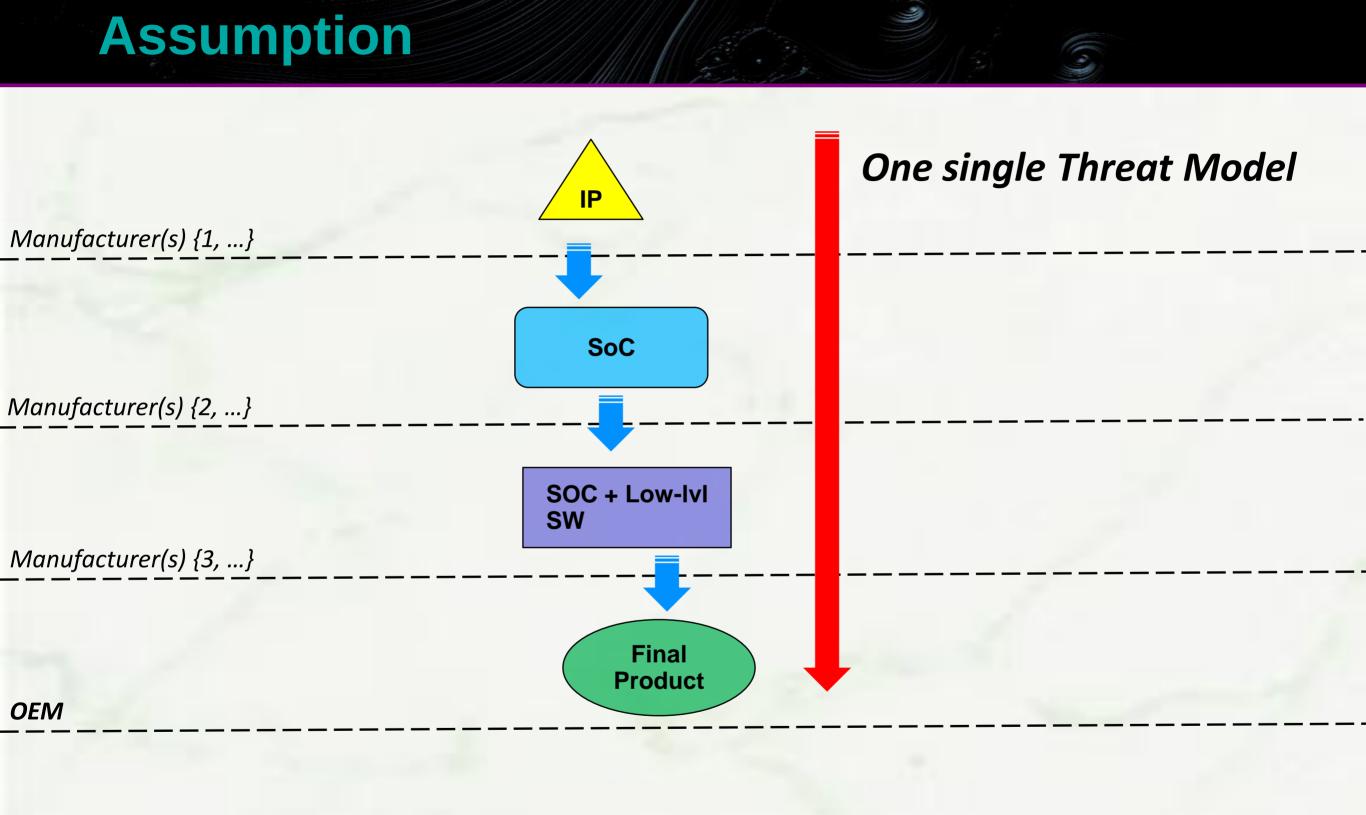

# Device == ecosystem effort → PRODUCT

- Each component in the chain has its own:

- Threat models, use cases and *assumptions*

### "Assumptions at boundaries may cause systemlevel vulnerabilities"

### "A few recurring classes (out of my experience)..."

# Completeness

### **Assumption of Completeness**

### "Component-level information is **sufficient** for characterizing security impacts on the final system"\*

\* Applies both to design and security assessments

### **Example: SW security assessment**

- A strcmp() classic implementation

- Taken from open-source project uClibc-ng

- Aimed at embedded devices

- Latest available version: v1.0.31

- Full source code available

### Any vulnerability?

```

31

int strcmp (const char *p1, const char *p2)

32

ſ

33

register const unsigned char *s1 = (const unsigned char *) p1;

34

register const unsigned char *s2 = (const unsigned char *) p2;

35

unsigned reg char c1, c2;

36

37

do

38

c1 = (unsigned char) * s1++;

39

40

c2 = (unsigned char) * s2++;

41

if (c1 == ' \setminus 0')

42

return c1 - c2;

43

44

45

while (c1 == c2);

46

47

return c1 - c2;

48

```

https://elixir.bootlin.com/uclibc-ng/v1.0.31/source/libc/string/generic/strcmp.c

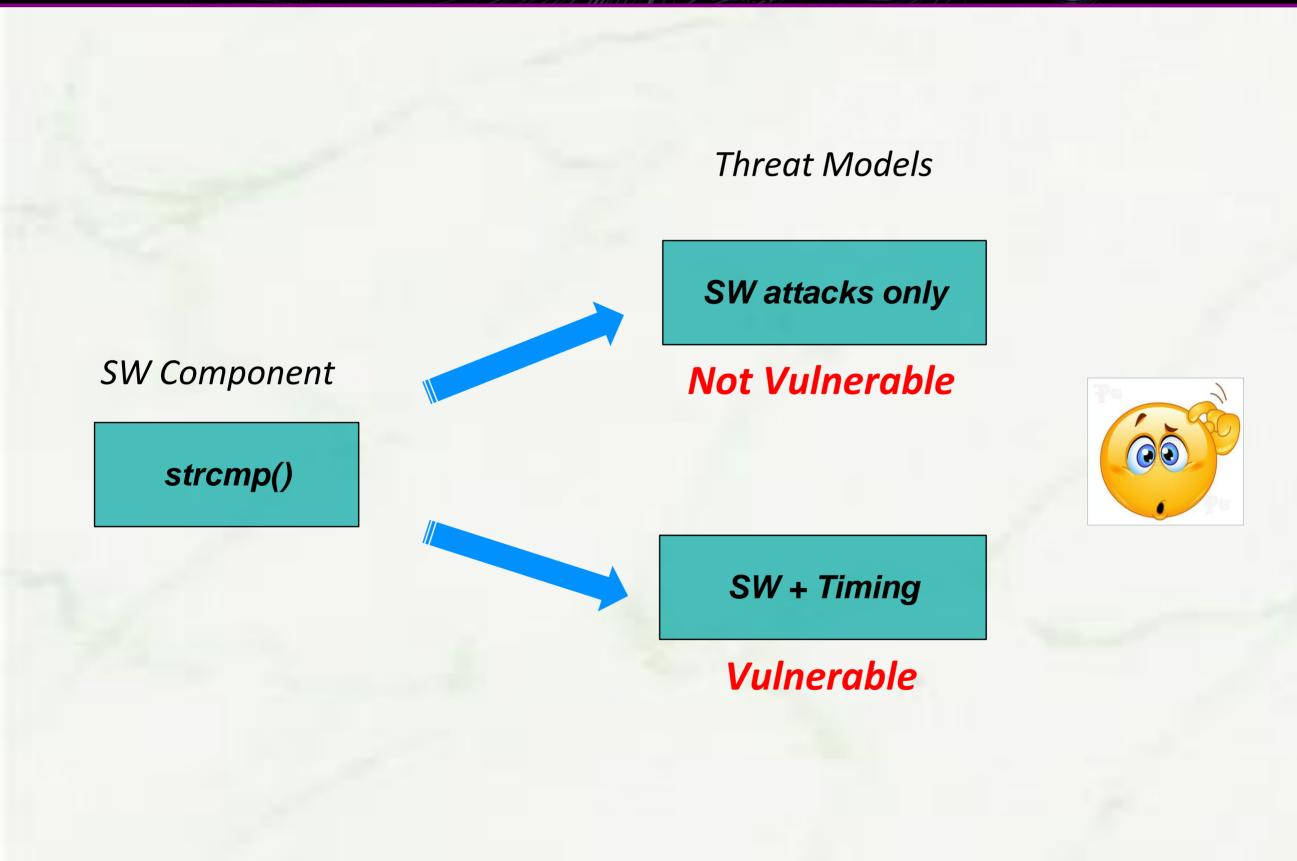

#### Threat model (TM): only SW attacks

Not vulnerable

#### But...

int strcmp (const char \*p1, const char \*p2) 31 32 33 register const unsigned char \*s1 = (const unsigned char \*) p1; 34 register const unsigned char \*s2 = (const unsigned char \*) p2;35 unsigned reg char c1, c2; 36 37 do 38 { Early 39 c1 = (unsigned char) \*s1++; 40 c2 = (unsigned char) \*s2++; termination 41 if (c1 ==  $' \setminus 0'$ ) 42 return c1 - c2; 43 44 while (c1 == c2);45 **Timing attack** 46 47 return c1 - c2; 48

https://elixir.bootlin.com/uclibc-ng/v1.0.31/source/libc/string/generic/strcmp.c

#### What about now?

- If attacker is able:

- to access a measurable channel

- to sample with sufficient precision

- If compared quantity is a security asset:

- e.g. A password, a MAC,...

Depends on the system.

Vulnerable

# **OK...which Threat Model applies?**

6

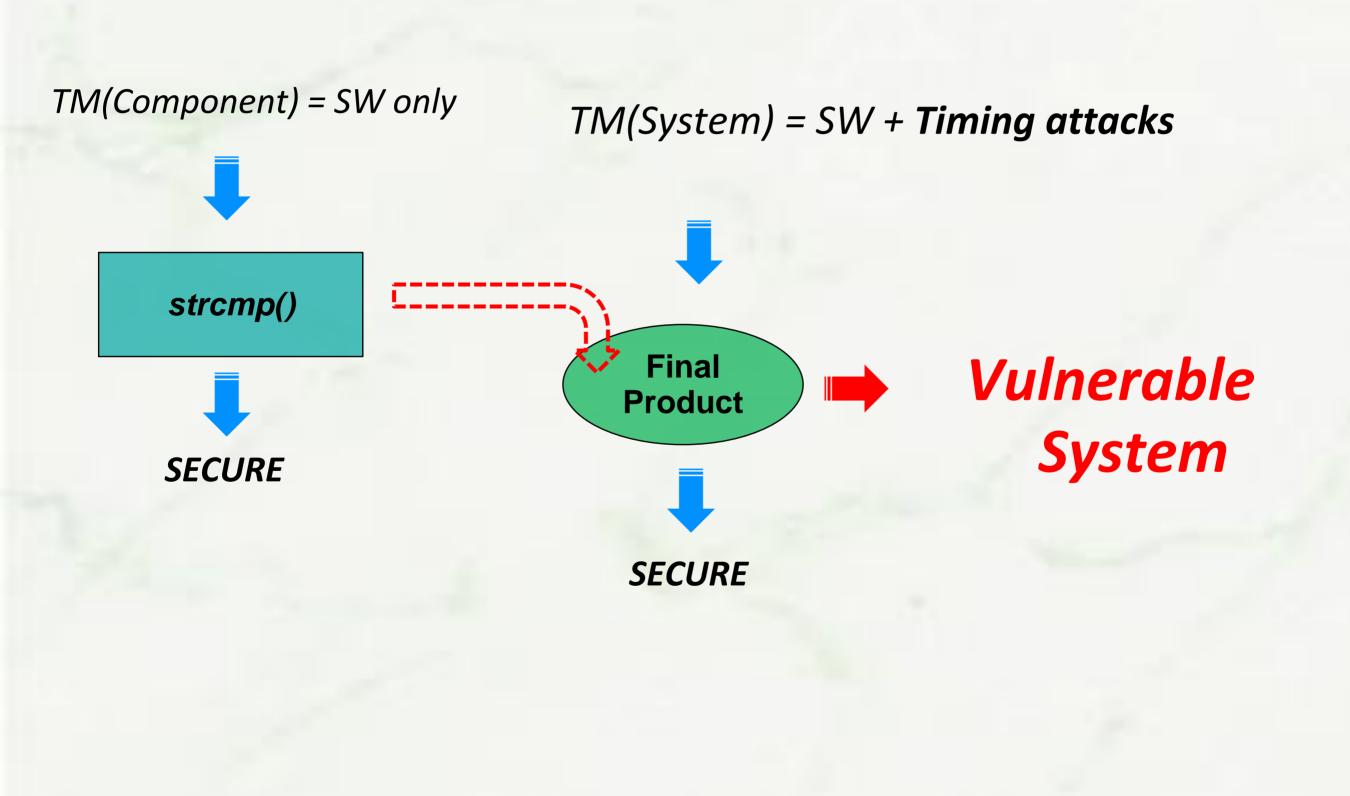

## Secure component → Vulnerable system

#### **Remarks: Vulnerability**

- Component level information insufficient

- Vulnerability cannot be assessed at component level

Depends on final system Threat Model

- Code review does not solve the problem

- Unless a Threat Model is specified

- Only "next stage" integrators are able to assess vulnerability:

- E.g: OEMs at the final product integration

### **Exploitability?**

- String comparison:

- "Impractical in the vast majority of cases" 2015 Morgan & Morgan

- Remote servers with fast CPUs

But... IoT systems are much slower!

that differ in the first character vs. strings that differ only at the 10th character. This indicates that timing attacks on regular string comparison have to be assumed feasible for any embedded system. \*

\* 2014 – Mayer, Sandin – "Time Trial"

- Target: Arduino UNO

- Clock speed: 16 Mhz

- Media: Ethernet 100Mbit

- Numeric PIN: 8 digits

```

Candidate password: 31337890

Verifying: 31337890

Success!

Verification successful!

Password found!!!

[+] Attack Completed

Total requests: 68002

Bruteforce complexity: 100000000

Ratio: 0.07%

```

(Live demo: Come tomorrow at HITB Armory!)

#### **Remarks: Exploitability**

- Exploitability cannot be assessed at component level

- Even with full source code

- Impact depends on final system:

- E.g. Clock speed, measurable channels,...

#### Full impacts can be established only at final product integration

### **Assumption of Completeness**

# "Component-level information is **sufficient** for characterizing component security impact on the final system"\*

\* Applies both to design and security assessments

#### Always ask for...

- Threat Model

- Existing development security processes:

- SDLC, Design security reviews, Source code audits, Product Penetration Testing

- Existing in-field security processes:

- Security fixes, Security maintenance (e.g. Firmware update for 5 yrs),...

- Security evaluation reports

### "When buying components, you are also buying risks"

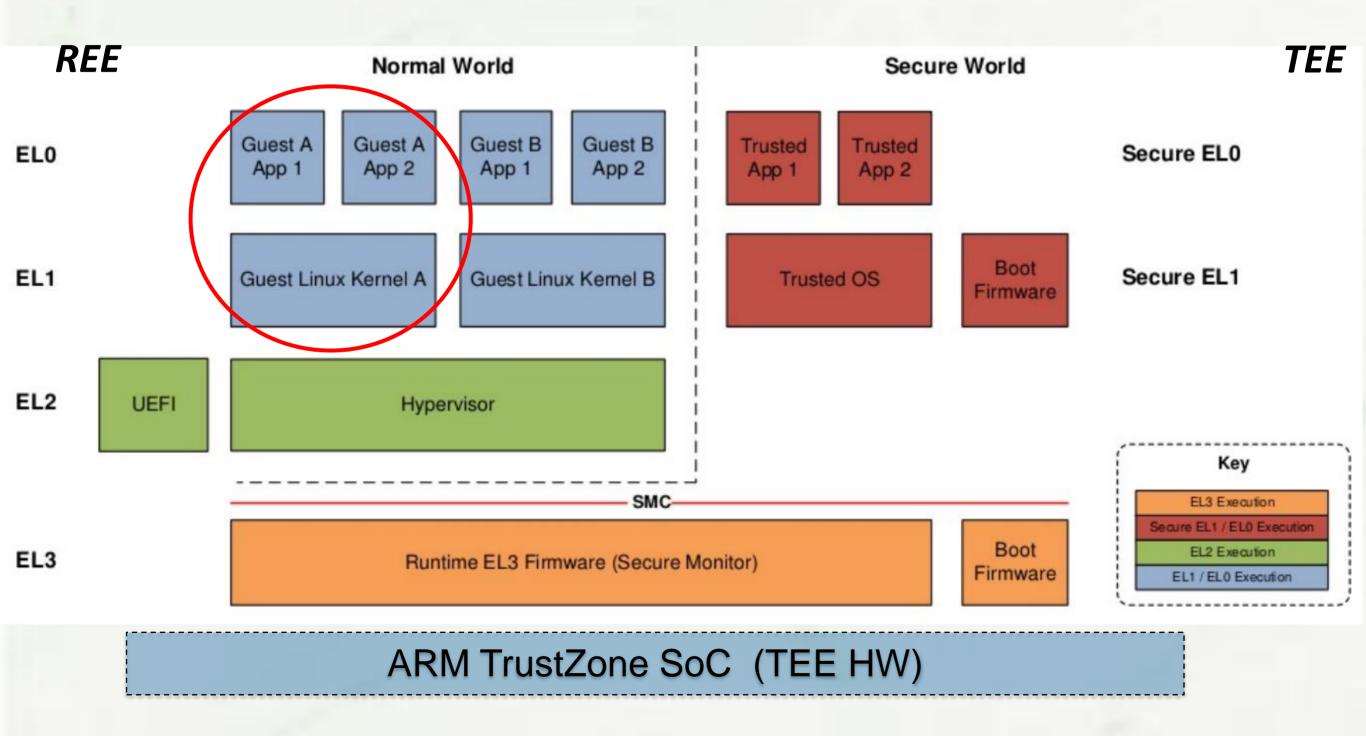

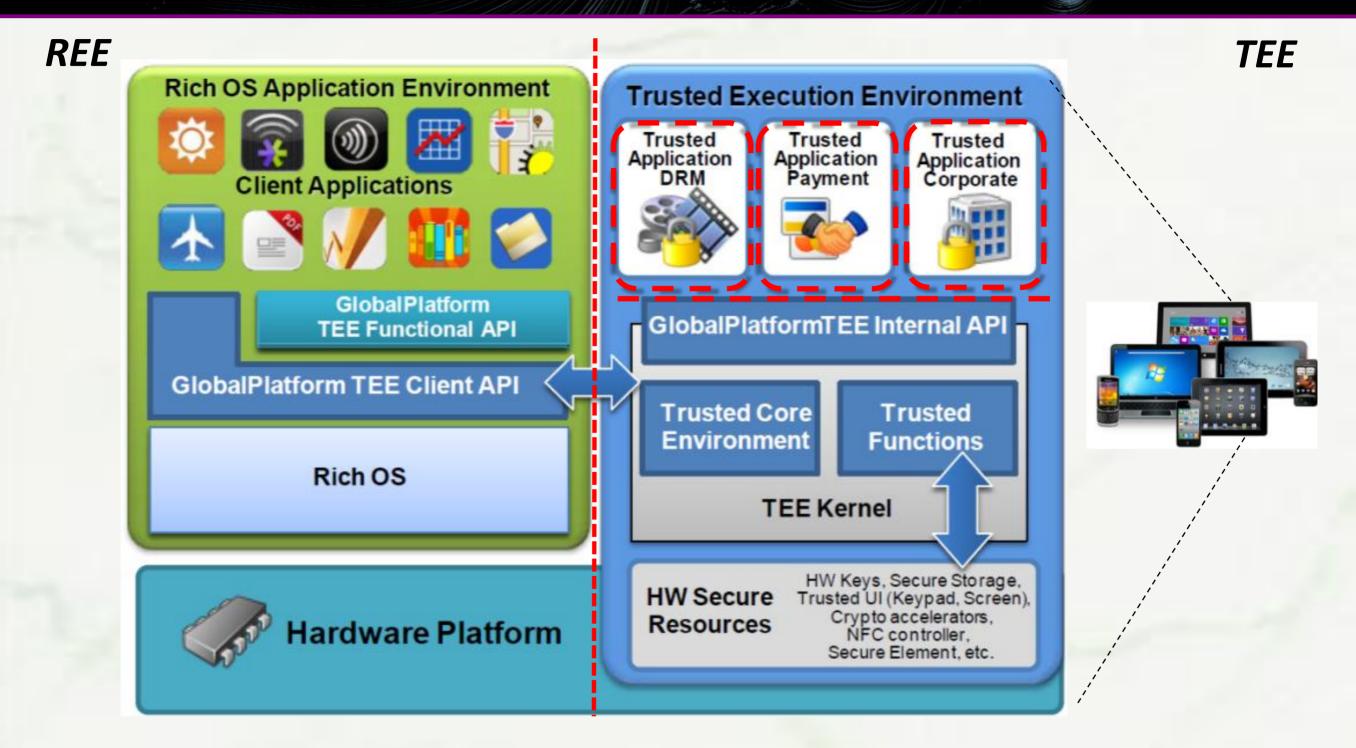

# A good example: ARM TrustZone

#### — Note

TrustZone technology is designed to provide a hardware-enforced logical separation between security components and the rest of the SoC infrastructure.

Lab attacks are outside of the scope of the protection provided TrustZone technology, although a SoC using TrustZone can be used in conjunction with an ARM SecurCore<sup>®</sup> smartcard if protection against physical attacks is needed for some assets.

#### **Threat Model specified in documentation**

# Correctness

### "The system will always behave as intended. Correctly executing as specified."\*

\* Applies both to design and security assessments

#### "Introducing faults in a target to alter its intended behavior."

- A controlled environmental change leads to altered behavior in a target

- Leverage a vulnerability in a hardware subsystem

### **Assumption: Expensive**

#### **Chipwhisperer Lite**

~\$250

# Microcontroller

< \$30

**FPGA**

~\$99

Also "Cheapscate: Attacking IoT with less than \$60" - Raphael Boix Carpi

VCC glitching cost (\$): < 300

- Physical access is required:

- Wrong. SW-initiated FI attacks can be performed remotely:

- Rowhammer and CLKSCREW

- No security decision point → Nothing to attack:

- Wrong. New fault models allow for direct code exection.

- We have countermeasures in SW:

- *Wrong*. New fault models can completely bypass SW FI countermeasures

- Our secure boot is encrypted. You need a key anyway:

- Wrong.

- Wait a minute. 🙂

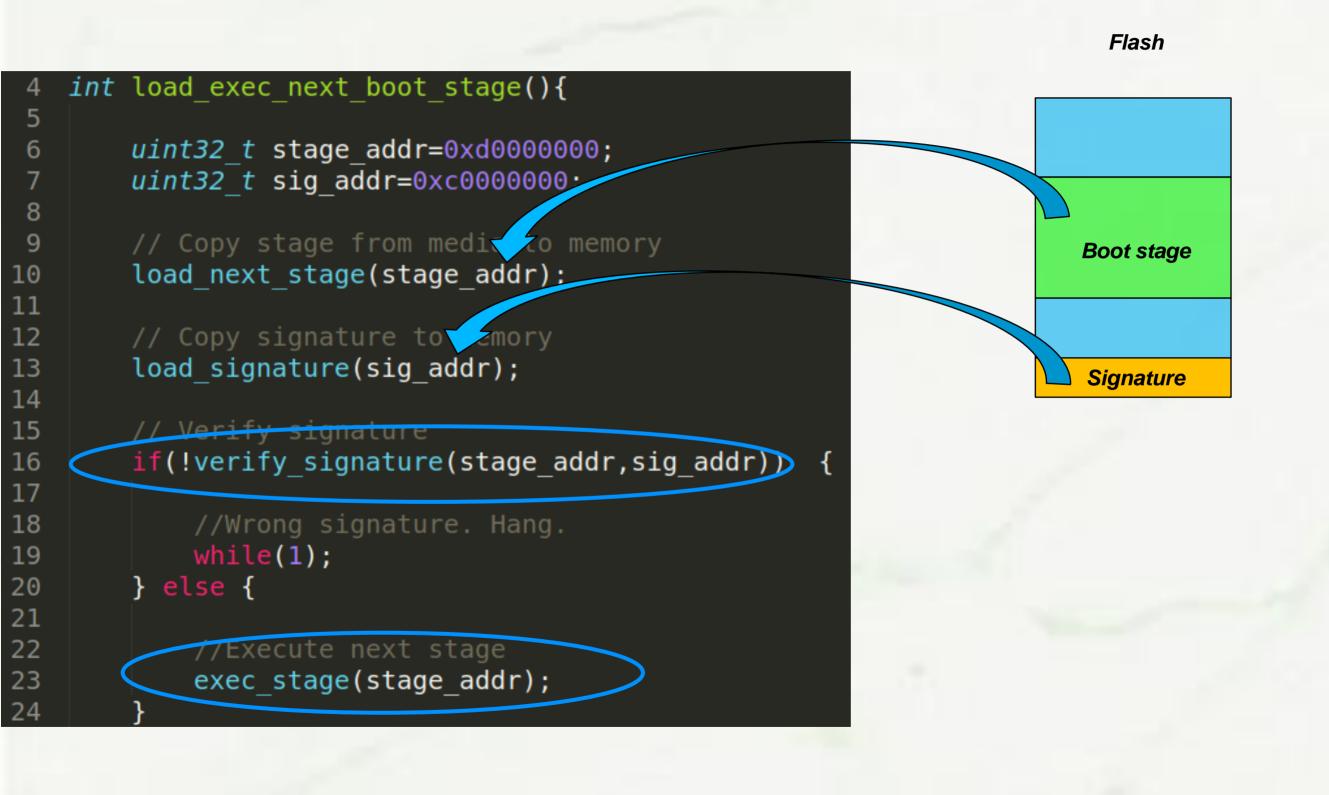

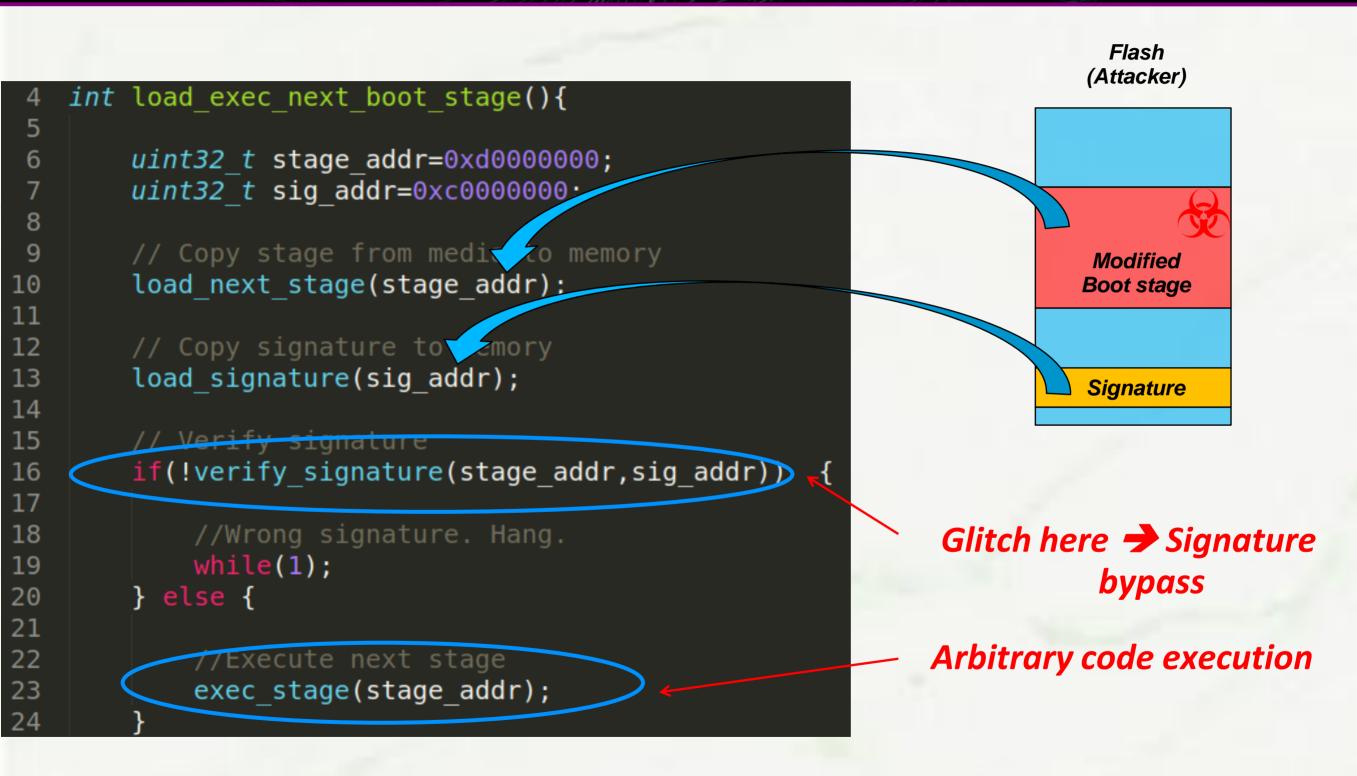

#### **Textbook attack**

#### "Instruction skipping"

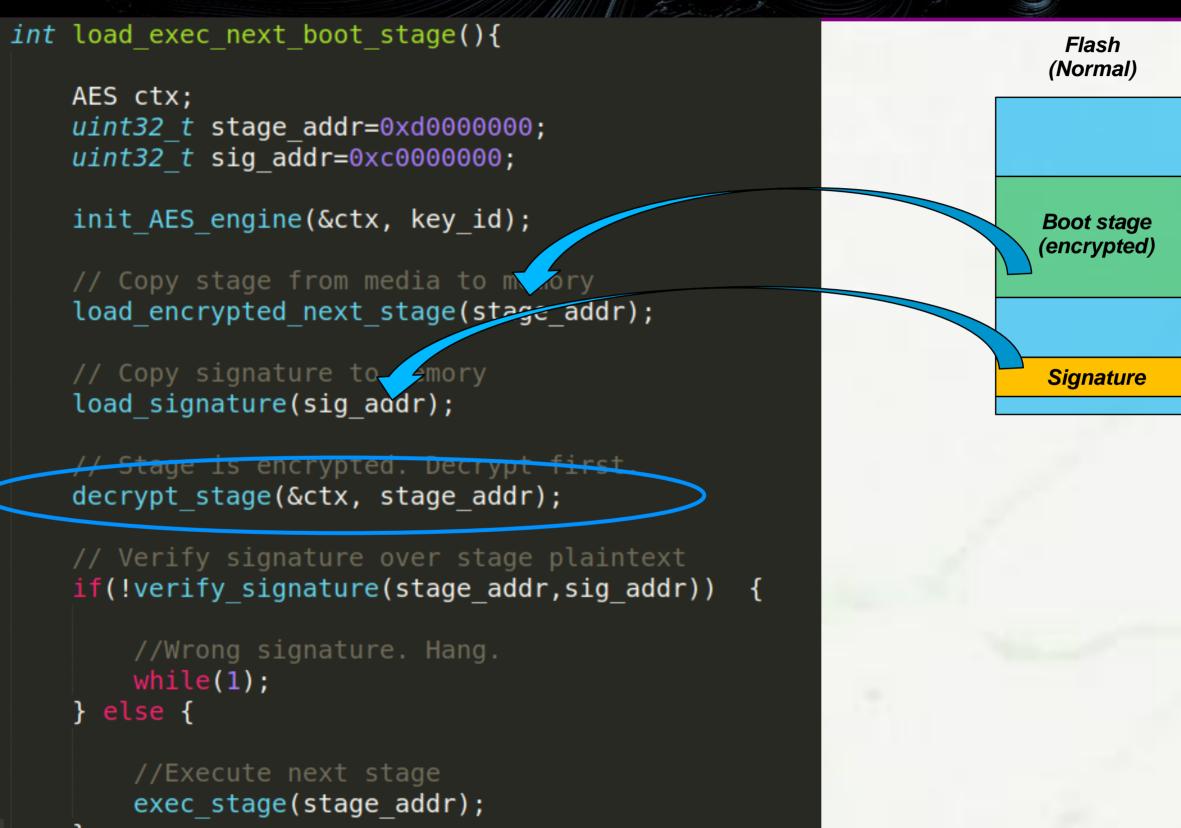

### **Encrypted Secure Boot**

20<

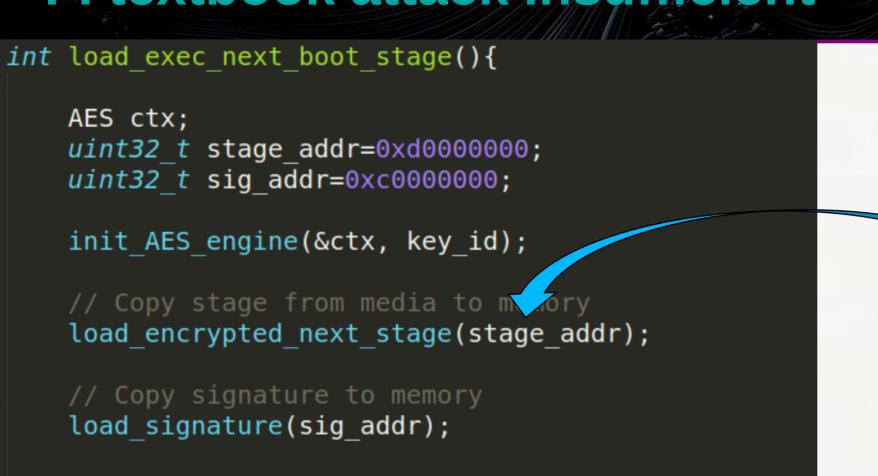

#### FI textbook attack insufficient

// Stage is encrypted. Decrypt first.

decrypt\_stage(&ctx, stage\_addr);

// Verify signature over stage plaintext

if(!verify\_signature(stage\_addr,sig\_addr))

//Wrong signature. Hang.

while(1);

} else {

//Execute next stage

exec\_stage(stage\_addr);

#### Unknown encryption key

Signature bypass useless

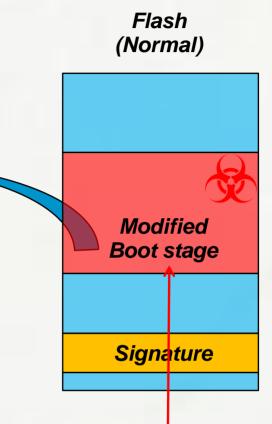

# **Creating execution primitives...out of thin air**

- ARM32 has an interesting ISA

- Program Counter (PC) is directly accessible

#### **Valid ARM instructions**

| MOV r7,r1      | 0000001  | 01110000 | 10100000 | 11100001 |

|----------------|----------|----------|----------|----------|

| EOR r0, r1     | 0000001  | 00000000 | 00100000 | 11100000 |

| LDR r0, [r1]   | 00000000 | 00000000 | 10010001 | 11100101 |

| LDMIA r0, {r1} | 0000010  | 00000000 | 10010000 | 11101000 |

#### **Corrupted ARM instructions may directly set PC**

| MOV pc r1<br>EOR pc r1            | 0000001 | <u>1</u> 1110000 | 10100000 | 11100001 |

|-----------------------------------|---------|------------------|----------|----------|

| EOR pc r1                         | 0000001 | <u>1111</u> 0000 | 00101111 | 11100000 |

| LDR pc [r1]                       |         | <u>1111</u> 0000 |          |          |

| LDR pc [r1]<br>LDMIA r0, {r1, pc} | 0000010 | <u>1</u> 0000000 | 10010000 | 11101000 |

#### Attack variations (SP-control) also affect other architectures

### **ROM code: secure boot + encryption**

int load\_exec\_next\_boot\_stage(){

AES ctx; uint32\_t stage\_addr=0xd0000000; uint32\_t sig\_addr=0xc0000000;

init\_AES\_engine(&ctx, key\_id);

// Copy stage from media to k mor load\_encrypted\_next\_stage(stage\_addr);

// Copy signature to memory

load signature(sig addr);

// Stage is encrypted. Decrypt first.

decrypt\_stage(&ctx, stage\_addr);

// Verify signature over stage plaintext

if(!verify\_signature(stage\_addr,sig\_addr)) {

```

//Wrong signature. Hang.

while(1);

} else {

```

//Execute next stage

exec\_stage(stage\_addr);

Flash (Attacker)

Glitch while loading pointers → PC set to pointers → Code exec at stage\_addr\*

#### Never executed

\*also see [FDTC 2016]: Timmers, Spruyt, Witteman

- FI vulnerabilities located at physical level

- Cannot be identified via HW or SW code review

- Only testing the real implementation can provide indications of vulnerability

- Testing better performed right after silicon integration:

- e.g. SoC Manufacturer

- Vulnerable HW may affect entire classes of devices

### **Assumption of Correctness**

## "The system will always behave as intended. Correctly execution as specified."\*

\* Applies both to design and security assessments

### FI in your threat model?

- Ask your SoC manufacturer for Security evaluation reports:

- Do NOT rely only on HW/SW audits only

- Only testing can uncover FI vulnerabilities

## "Either you have countermeasures, or... ...you are painfully, **desperately vulnerable**"

## Consistency

### "The entire system has only one threat model and protects the same assets."

Feasible?

### A typical Security Model...

6

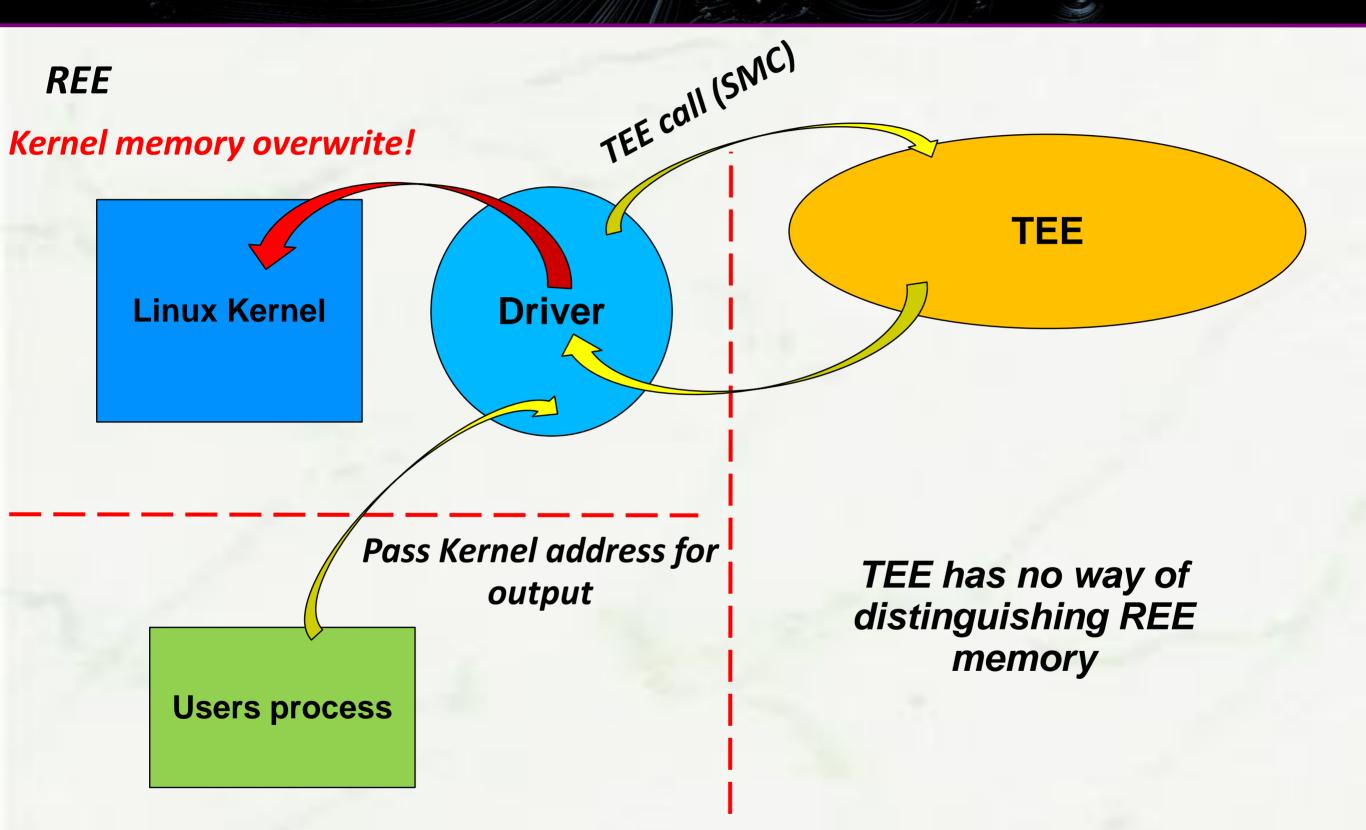

### ...with a TEE

0

### **TEE security model**

No intention to protect REE...

### BlackHat 2015

- Different security models may be present at the same time

- May not be aware of each others

- May be leveraged AGAINST each others

### **Assumption of Consistency**

### "The entire system has only one threat model and protect the same assets."

### Recommendations

- Understand components' Security Model

- Does it fit with your Security Model?

- Evaluate within system Threat Model

# "There may be no consistency, across components and subsystems."

...expect none...

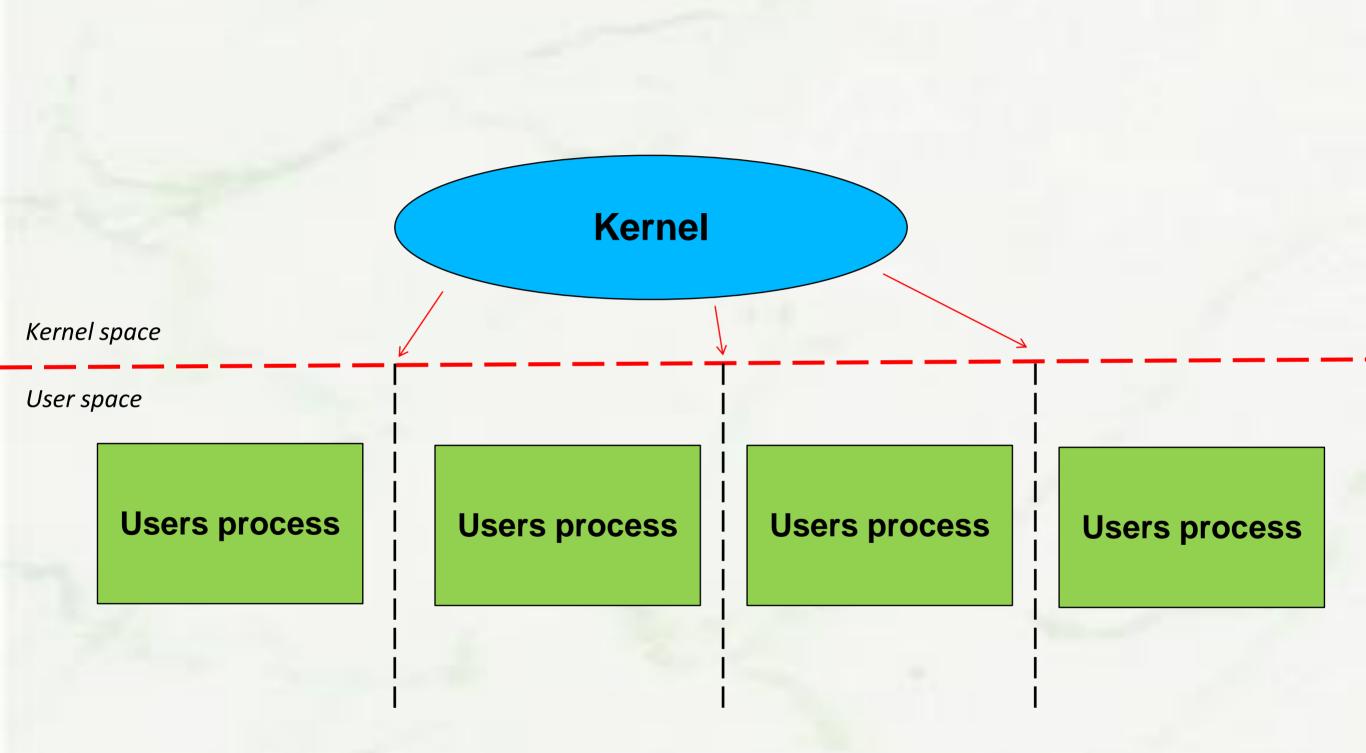

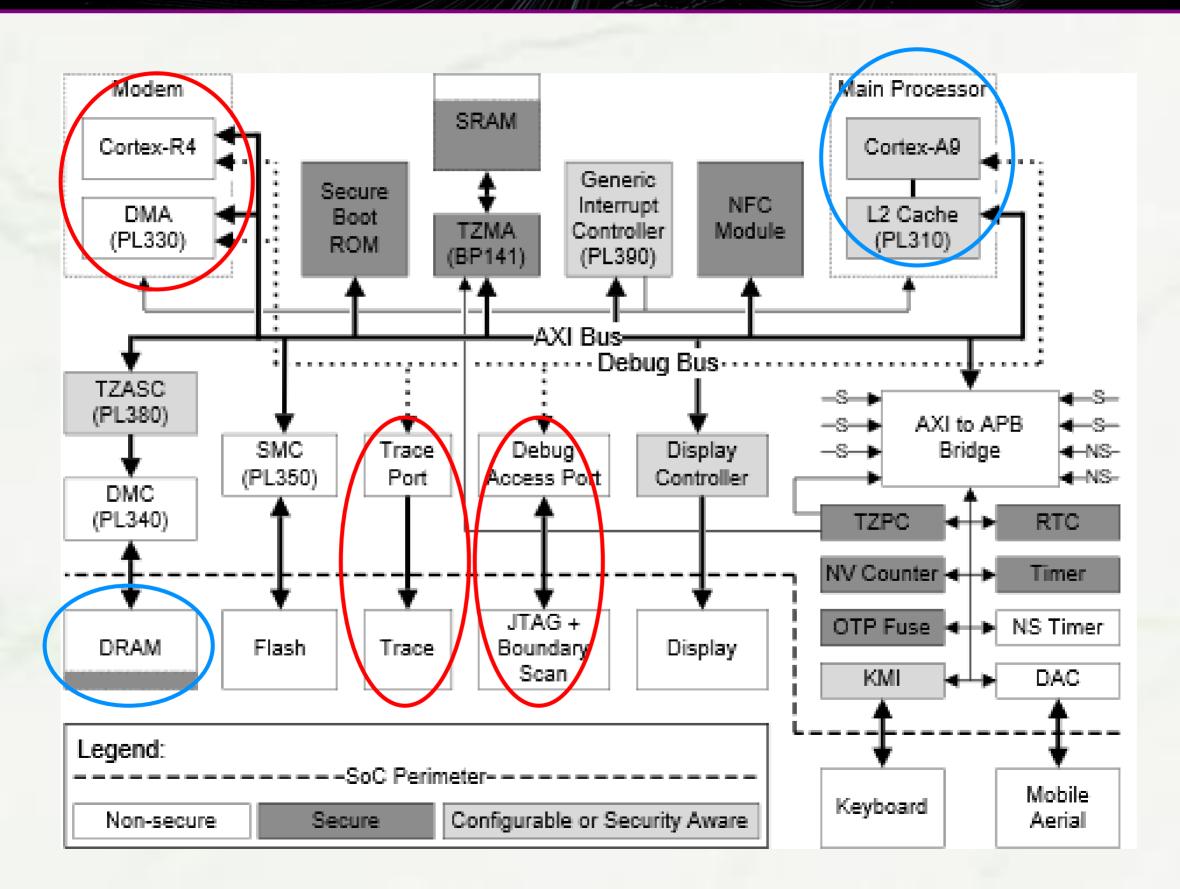

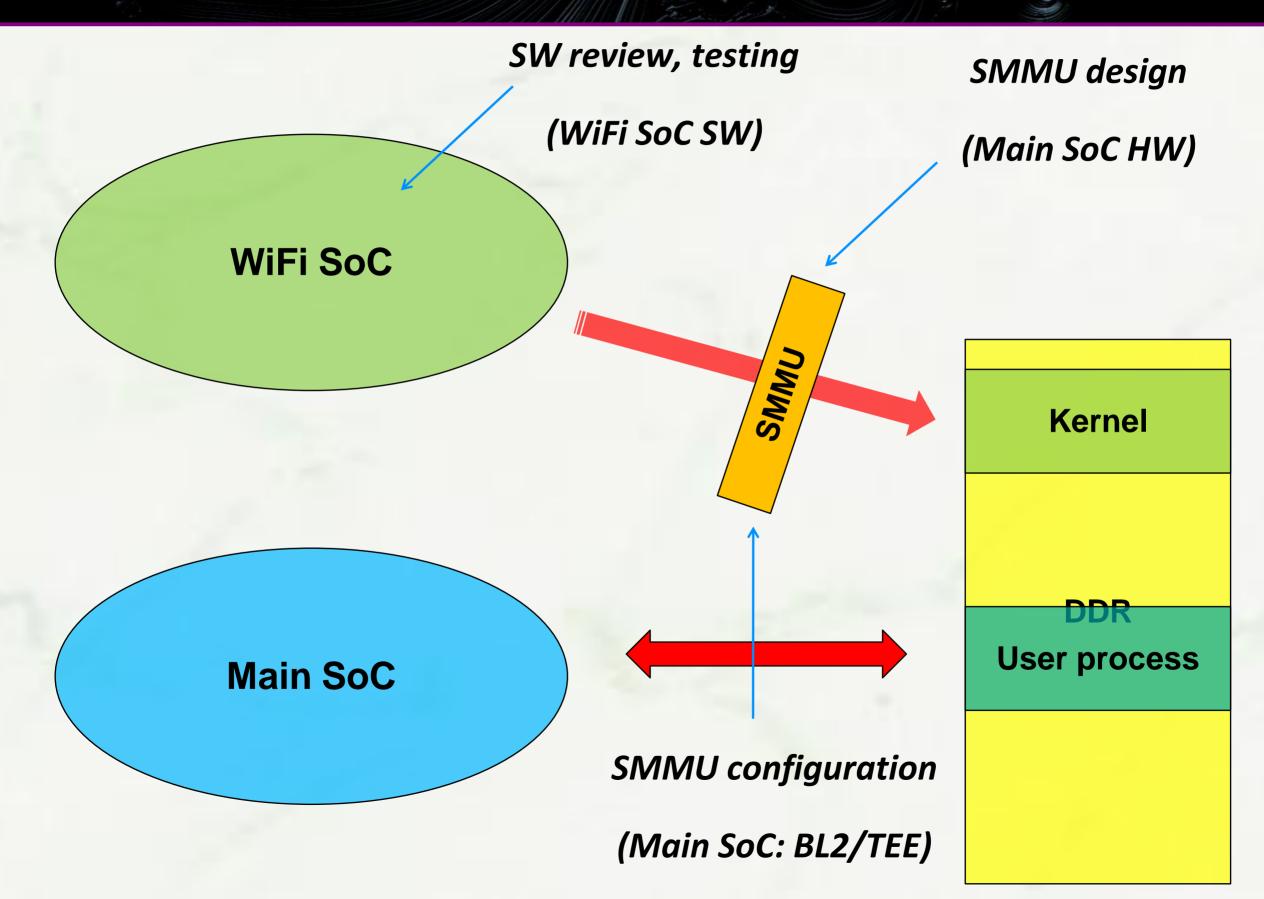

## Isolation

### Assumption of Isolation

# *"There is only sub-system. Mine"*

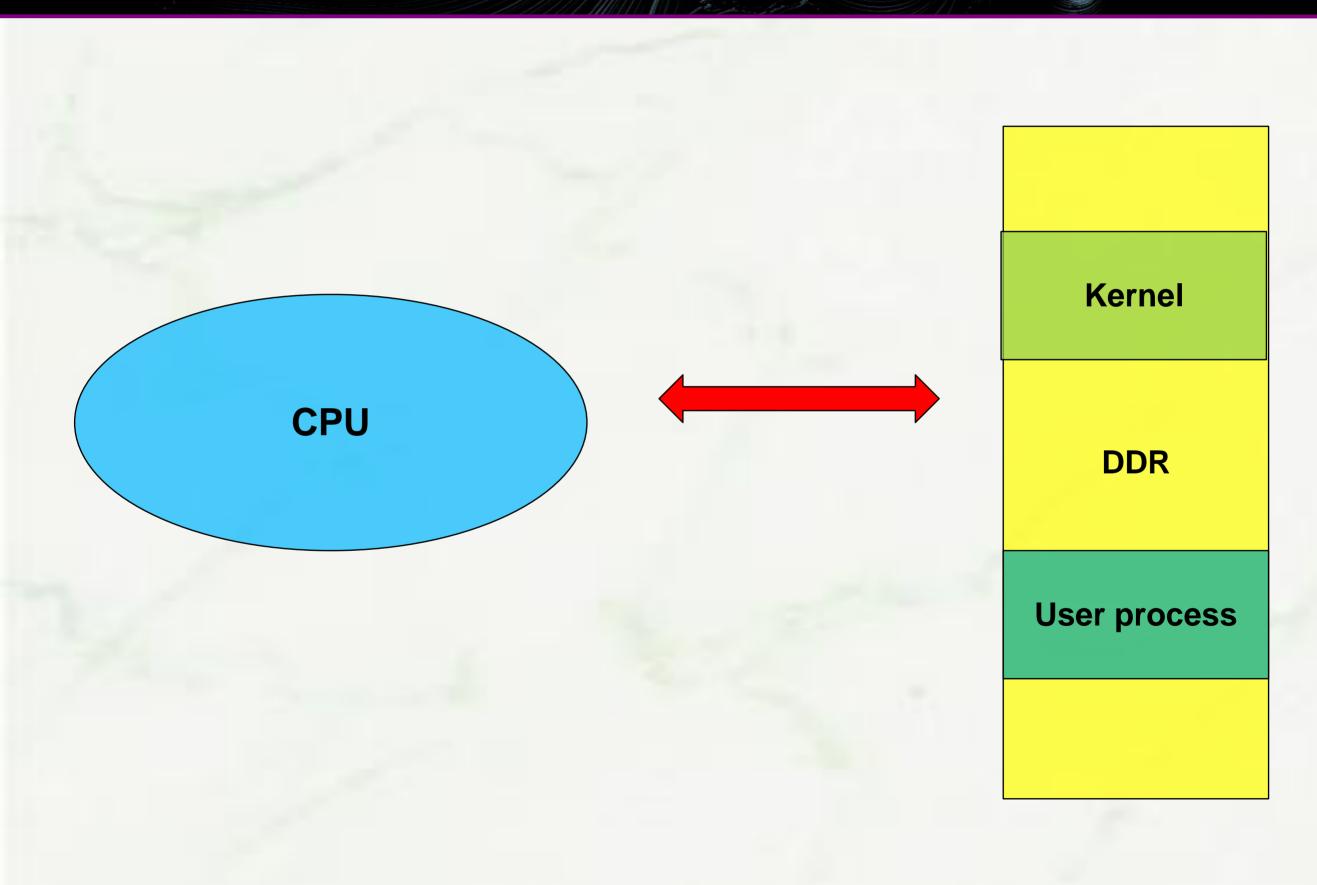

### A simplistic model

6

### **Reality: other IPs can access DDR**

-

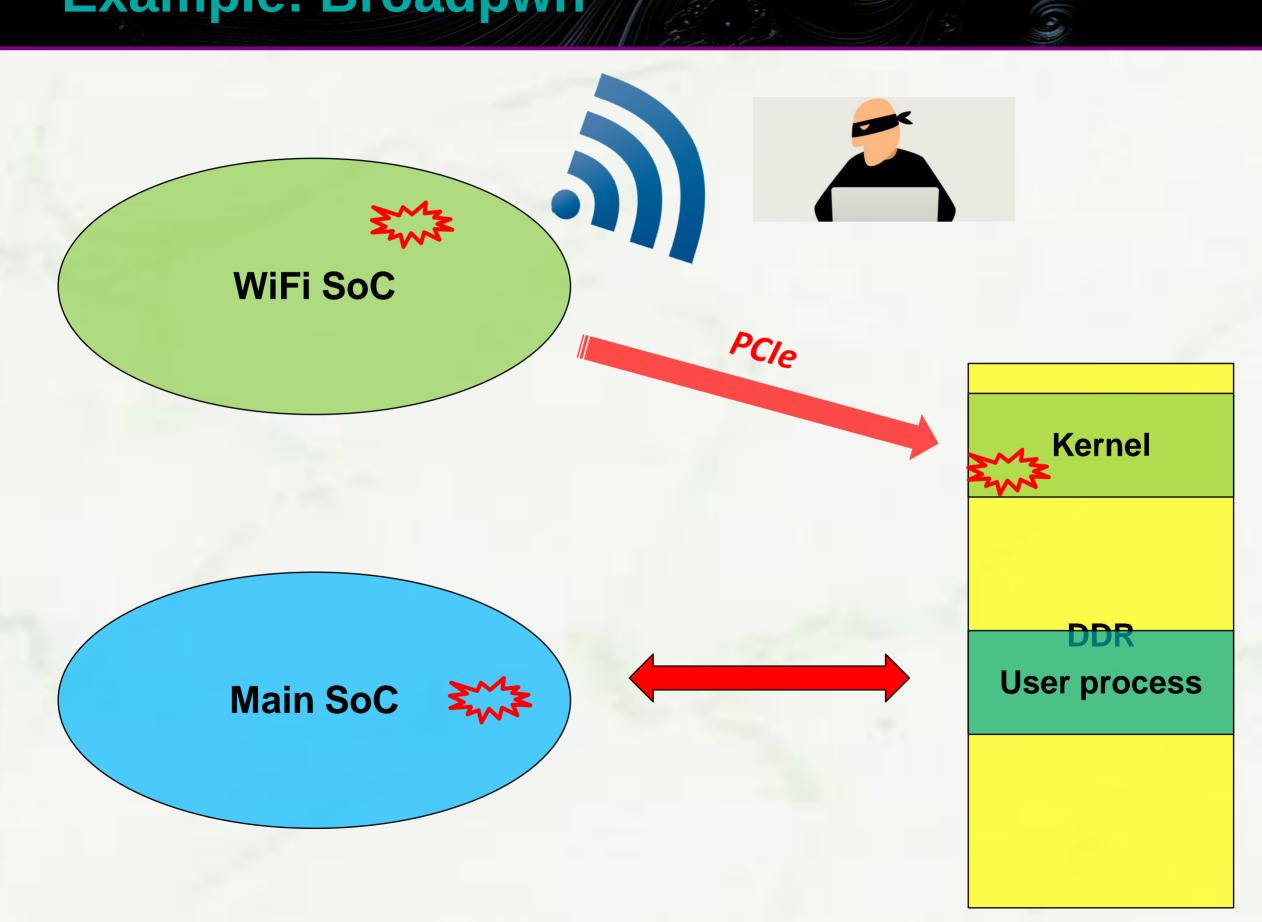

### **Example: Broadpwn**

#### Remarks

- SoCs → "execution units"

- Other SoCs may have access to Main SoC DDR

- May not be aware of each others' Security Models:

- Kernel vs userspace in SoC1 → Plain addressable memory for SoC2

### What could have been done?

### And we are missing...

- Other execution units:

- Audio/Video Processors

- GPUs

- Power Modules

- ...

- DMA-capable IPs:

- USB

- Firewire

- PCMCIA

- PCIe

Other Bus masters IPs

There can be hundreds...

### Assumption of Isolation

## There convicus-system. Mine

Bus masters My God, It's full of stars....

0

## Conclusions

### Reflections

- System Security:

- Threat Models may differ between Components

- -

Security(System)  $\equiv \sum_{i}$  Security(Component<sub>i</sub>)

- Security Evaluation: •

- Context and system-level information required for assessment

- Code reviews cannot identify all vulnerabilities (e.g. FI)

- Design:

- HW and SW must cooperate. Across the whole system.

- Regardless of Manufacturer, Department, Teams boundaries

- Protect FROM other sub-systems

"Unchecked assumptions at boundaries can be fatal"

### Recommendations

- Estabish a system-level threat model:

- Apply and verify consistency everywhere

- For every HW/SW component:

- Gain understanding of use case and threat models

- Test and review thoroughly

- Security assessment and testing MUST consider:

- System Threat Model

- For every 3<sup>rd</sup> party component ask:

- 1. Threat Model

- 2. Security practices and processes

- 3. A security evaluation report

- You are already paying for it.

## PULSE

### **Cristofaro Mune**

### **Product Security Consultant**

<u>c.mune@pulse-sec.com</u>